こんにちは、スクーティー代表のかけやと申します。

弊社は生成AIを強みとするベトナムオフショア開発・ラボ型開発や、生成AIコンサルティングなどのサービスを提供しており、最近はありがたいことに生成AIと連携したシステム開発のご依頼を数多く頂いています。

半導体設計における仕様情報の整理は、複雑で時間のかかるプロセスです。特に自動車、防衛、航空宇宙、AIアプリケーション向けの高度なチップ設計では、データの整合性と効率的な管理が不可欠となります。多くの企業が設計データの管理に苦労しており、データの一元管理や効率的なアクセス方法を模索しています。

この記事では、リライト元記事に記載された各種仕様情報、設計データ、プロトコル情報を基に、最新のベストプラクティスを盛り込みつつ、各セクションごとに詳細な背景説明や具体例を追加し、エンジニアにとって有益な情報を網羅的に解説します。特に具体的な数値やベストプラクティスについて、箇条書きや図表を交えて分かりやすく説明しています。

半導体設計データ管理の基礎

まず、OCR について知りたいという方は、ぜひこちらの記事を先にご覧ください。

関連記事:Tesseract OCRの完全解説:インストールから活用事例、最新技術との比較まで

関連記事:olmOCR : PDFテキスト抽出を1/32のコストで実現!?

関連動画:【2025最近】知らなきゃ損!電子部品カタログ作業を生成AI-OCRで90%効率化する方法

半導体仕様情報の多様性

半導体仕様情報は、集積回路(IC)の設計から製造までの各フェーズにおける膨大なデータの集合体です。これには、顧客が要求する設計仕様、各回路設計で利用される回路図設計データ、製造工程で求められるレイアウトデータ、シミュレーションにより作成される各種テストベクトルやタイミング解析、電力・熱・EMI/EMC解析などのシミュレーションデータが含まれます。また、PDK(プロセス開発キット)データや、企業が所有する知的財産(IP)ライブラリ、設計仕様に関するドキュメントと部品表(BOM)、そして設計プロセスを管理するためのメタデータなどが存在します。

各種データは、IC設計のフロントエンドからバックエンドの各段階で不可欠な情報を提供し、エンジニアが迅速かつ正確に必要な情報へアクセスできるよう、体系的かつ統合的な管理手法が求められています。システム全体でのデータ正確性が担保されなければ、設計品質や製造工程の効率が大幅に低下するため、設計段階での厳格なバージョン管理と各種シミュレーション結果の統合は非常に重要となります。

例えば、設計仕様間に不整合が生じた場合、回路図やレイアウト各部で誤差が累積し、最終製品へ影響を及ぼすため、各工程での情報更新と修正が欠かせません。こうした複雑な情報群を漏れなく管理し、各工程でのトレーサビリティを確実にするためには、高度なデザインデータ管理システムの導入が不可欠であり、システム自体の柔軟性や拡張性が設計の最終成果に大きく影響する要素となっています。さらに、現代の半導体設計は大規模プロジェクトとなっており、各設計者間のリアルタイム共有が求められるため、仕様情報の正確な管理はプロジェクト全体の成功に直結しています。また、今後の技術進展によりデータがさらに増加するため、常に最新の管理手法を採用して更新する必要があります。

膨大な設計仕様やシミュレーション結果、各種ドキュメント管理で「人手による情報収集」にお困りではありませんか?生成AI-OCRサービスなら、100ページを超えるPDF資料からも自動で仕様情報を抽出し、一覧化できます。人力コピー作業から解放され、情報の正確性もアップ。工数削減とスピードアップを同時に実現しませんか?

設計仕様の重要性

設計仕様は、ICが実行すべき機能や性能の詳細な記述を含む最も基本かつ重要なドキュメント群です。具体的には、動作速度、消費電力、放熱特性などの性能指標が明確に記載され、ターゲットとなるアプリケーションや使用環境に応じた機能要求が定義されています。これらの設計仕様を基礎として、回路図設計や物理設計のレイアウトが進められ、各種シミュレーションによるパフォーマンス試験が実施されます。初期段階での仕様の精度と一貫性はプロジェクト全体に大きな影響を与え、仕様があいまいまたは頻繁に変更されると、設計全体で不整合が生じ、検証フェーズに重大な問題を引き起こす可能性があります。

また、正確な設計仕様は、各種EDAツールやシミュレーションソフトが定められたパラメータに基づいて正確な解析を行うための基盤となります。例えば、わずかな性能指標の違いが大規模回路全体に影響を及ぼす場合、正確な仕様情報が設計者にとって最も重要な指針となり、エラー発生のチェックポイントとして機能します。

さらに、政府のCHIPS法などの政策が示すように、設計の信頼性向上のために各国が戦略的に取り組む背景には、正確な設計仕様の管理と維持があるため、これら文書の厳格な管理は市場競争力を左右する重要な要素です。したがって、設計仕様は単なる出発点ではなく、品質、リードタイム短縮、最終製品の信頼性向上の不可欠な基盤となっています。プロジェクト進行中には、仕様変更が生じた際に影響範囲を迅速かつ正確に把握し、各段階で適切に反映する仕組みが必要です。

回路図設計データの管理

回路図設計データは、ICの基本機能を視覚的に表現する重要な情報源です。設計者は、標準化された記号やシンボルを用いて各コンポーネントの接続状態や動作原理を図式化し、複雑な回路ネットワーク全体の構造と信号の流れを把握します。回路図は物理的レイアウトデータへの変換前の段階であり、その正確性が後工程の製造やシミュレーションに直接影響するため、各変更が厳密に記録され、バージョン管理が徹底される必要があります。分散した複数の設計チームが同一回路図にアクセスして変更を加える際には、差分や変更履歴を正確に追跡するシステムが不可欠です。

また、回路図に基づく各種シミュレーションやタイミング解析は最終的な物理設計に大きな影響を与えるため、回路図管理体制は設計品質維持と効率的な問題解決のために極めて重要です。さらに、各コンポーネントの接続情報が正確に反映されることで、不具合の早期発見や設計変更時の影響範囲把握が容易となり、結果的に設計コストと工程短縮に寄与します。自動チェック機能と設計ツール連携により、回路図の変更がリアルタイムに反映される仕組みは、全体の設計フローの効率化および将来的な設計変更への柔軟な対応基盤となっています。

レイアウトデータの詳細管理

レイアウトデータは、IC設計の物理的実現を可能にするための具体的なパターン、形状、設計ルールを記録した情報です。GDSIIやOASISなどの標準ファイル形式で管理され、各レイヤーの寸法や配置、設計ルールが正確に記録されることで、製造工程でのフォトマスク作成の基礎となり、最終製品の製造品質に大きく影響します。もしレイアウトデータに不整合や誤差があると、製造プロセス中にパターンエラーや電気的特性の低下、不良品発生のリスクが高まります。各レイアウトファイルには詳細な設計ルールチェック(DRC)やコンパリソンチェックが行われ、各バージョン間の変更点が正確に記録される必要があります。

また、レイアウト管理は物理設計実現の保証だけでなく、後工程での検証データやシミュレーション結果と連動し、設計全体の品質向上に直結します。例えば、設計変更時に過去バージョンとの比較が容易になることで、エラー再発防止と迅速な修正が可能となり、プロジェクト全体のタイムライン管理に大きく貢献します。設計者が各レイヤーの物理的・電気的特性を定量的に評価できるよう、統合管理システムを通じた詳細な解析データが提供される仕組みは、設計信頼性と効率性の向上に寄与し、市場競争力を強化する基盤となっています。

シミュレーションデータの活用

IC設計において、シミュレーションデータは、回路が物理的に実装される前にその動作を検証するための必須情報です。設計者は、各種テストベクトルを用いて回路の動作条件を再現し、タイミング解析、電力解析、熱解析、EMI/EMC解析を通じて、設計が所定パフォーマンスを発揮するかを検証します。これにより、高価な物理プロトタイプ作成前に潜在的な問題を洗い出し、設計変更の必要性を早期に把握でき、全体の開発コストとリードタイムが大幅に短縮されます。

さらに、各シミュレーションデータは設計の妥当性を裏付ける客観的な証拠として活用され、後工程での検証や品質評価に寄与します。特にシフトレフト戦略により、設計初期段階で問題を検出できれば、その後の修正コストや再設計リスクを最小限に抑えることが可能です。シミュレーション環境は、複雑な条件下での動作確認を現実的かつ多面的に提供し、最新の解析結果に基づいた迅速な設計パラメータ調整を可能にするため、製品のパフォーマンスと信頼性向上に直結しています。

テストデータと検証プロセス

テストデータは、IC設計においてプレシリコンおよびポストシリコン検証フェーズで取得される重要な情報です。各種テストベクトルを用い、温度、電力、環境ノイズなどの条件下で回路が期待通りの応答を示すかを実験的に確認します。これにより、設計段階で見落とされがちな微細な不整合や潜在的なエラーが早期に明らかとなり、後工程での不具合発生リスクが大幅に低減されます。

さらに、テストデータは国際的安全基準や業界標準に基づく設計検証の決定的な証拠として活用され、自動車、航空宇宙、防衛といった高い安全性が求められる分野での厳密な検証において不可欠です。検証プロセスでは、各テスト結果を正確に記録し、設計データ管理システムと連動して変更履歴を詳細に保存するため、設計のトレーサビリティが確保され、問題発生時の迅速な原因究明が可能となります。これにより、エンジニアは即座に問題を特定し、必要な修正を反映できる基盤が整えられています。

プロセス開発キット(PDK)の役割

PDK(プロセス開発キット)データは、半導体製造プロセスにおける重要な情報源です。プロセス変動、リソグラフィ情報、使用材料や化学的特性など、詳細な情報を網羅しており、ICが実際の製造環境で期待通り動作するかどうかを予測するための指針を提供します。各製造ラインでプロセスの変動に柔軟に対応するため、PDKは頻繁に更新され、設計データ管理システムにシームレスに統合される必要があります。

これにより、設計者は最新の製造条件に基づいた迅速な設計検証が可能となり、結果として不良率低減、歩留まり向上、製造コスト削減が実現されます。PDKデータの管理は、設計と製造の連携を強化し、各種解析ツールとの連動によって、設計変更が製造工程に与える影響を正確に評価する仕組みとして機能しています。

知的財産(IP)ライブラリの管理

知的財産(IP)ライブラリは、IC設計における再利用可能な設計要素の集積地として、新規製品開発の効率化とリスク低減に寄与します。IPライブラリには、仕様書、ソースコード、設計ガイドライン、ライセンス情報などが含まれ、エンジニアは必要な情報を迅速に検索・統合できます。各IPブロックのバージョン管理や変更履歴の詳細な記録により、再利用時の不具合再発や設計ミスを防ぎ、設計全体の信頼性を向上させます。

また、厳格なセキュリティ対策によって知的財産が保護され、企業の技術優位性の維持にも寄与します。これにより、IPライブラリの管理プロセス自動化と各種承認プロセスの迅速化が図られ、設計プロジェクト全体のリードタイム短縮と品質向上に貢献しています。

ドキュメントと部品表(BOM)管理

IC設計において、設計仕様書、標準ドキュメント、ユーザーマニュアル、操作ガイドラインなどは、設計理解と実装に不可欠な情報源です。また、部品表(BOM)は、設計に必要なコンポーネントや部品、その他資料を網羅した詳細なリストであり、正確かつ最新の情報でなければ製造工程上のトラブルやコスト超過の原因となります。したがって、ドキュメントとBOMの管理は、設計データ管理システムの一環として厳格に管理され、各文書のバージョン管理や承認プロセスが自動化されることで、情報の正確性と一貫性が保証されます。各文書に付随するメタデータ(作成日時、改訂履歴など)も詳細に記録され、将来的なトレーサビリティや監査において有用な情報源となり、全体の設計過程の透明性と効率性を高めます。

設計仕様書やBOM、PDK資料のバージョン管理や情報更新に苦労していませんか?生成AI-OCRサービスなら、煩雑な設計ドキュメントの情報を一括抽出・管理し、常に最新情報へ瞬時にアクセス可能。レイアウトが複雑でも正確にデータ化できるので、二度手間・入力ミスから解放されます。「そろそろ手放したい…」と思ったらぜひご相談ください!

メタデータの活用

メタデータは、設計ファイル自体の属性情報を格納する重要なデータです。ファイル名、バージョン履歴、変更日時、設計パラメータ、作成者情報などが記載されることで、各設計ファイルの特性や変更履歴が詳細に追跡可能となり、膨大なデザインデータの中から必要な情報を迅速に抽出できます。

特に、複数エンジニアが同一プロジェクトに参加する場合、メタデータにより各データの出所や変更内容が明確となり、作業の重複や誤解、設計変更時の不具合再発防止に大きく寄与します。これらの情報が適切に管理されることで、設計プロジェクト各フェーズで迅速かつ正確な意思決定が可能となり、最終的な製品の市場競争力向上に直結します。

半導体設計管理の主要な利害関係者

企業の分類と役割

半導体設計データ管理では、関与する企業は大きく4つの主要グループに分類されます。ファブレス企業は設計に専念し、製造はサードパーティに委託。一方、垂直統合型デバイスメーカー(IDM)は設計から製造まで全工程を自社内で完結させます。

また、OEM(自動車メーカーやクラウドコンピューティングプロバイダーなど)は、特定用途や顧客ニーズに合わせたカスタマイズチップの設計を進め、EDA/IPベンダーは電子設計自動化ツールや再利用可能なIPコアを提供することで、全体の設計効率と精度向上を支援します。これら各企業が連携し各自の専門性を活かすためには、一元管理された設計データシステムと統一フォーマット、バージョン管理ルールの共有が不可欠であり、全体の品質と納期厳守に直結します。

システムオンチップ(SoC)設計の需要増加

システムオンチップ(SoC)などの高度で複雑な集積回路の需要が世界的に増加しており、IDMやファブレス企業は、各専門分野ごとに複数の設計センターやプロセスを整備する必要が高まっています。各設計チームは、特化したEDAやシミュレーションツールを活用し、各部門間の連携を図りながら全体の設計統合を実現しなければなりません。

こうした状況下では、一元化された設計データ管理システムが、異なるツール間のデータ互換性や各チーム間の連携を円滑にし、最終製品の品質均一化と納期管理に大きく寄与します。各設計センター間で常に最新情報がリアルタイムに共有される仕組みは、設計上の不整合や重複作業を大幅に防止し、企業全体の競争力向上の鍵となっています。

半導体データ管理の4つの重要なトレンド

デジタル変革の潮流

半導体業界では、デジタル変革が急速に進み、クラウド技術、リアルタイムデータアナリティクス、自動化ツールなどが設計データ管理戦略に大きな変革をもたらしています。大企業からスタートアップに至るまで、各組織が最新技術を採用し、効率的なデータ統合と解析環境を構築することで、シミュレーションデータやその他設計データの増加に対応しています。

これにより、設計工程全体で情報がリアルタイムに共有され、各フェーズの連携が強化され、製品市場へのリードタイムが大幅に短縮されています。例えば、シミュレーション時間が従来比50%短縮された数値的根拠も存在します。また、自動化ツールやAI技術の導入により、設計プロセスが合理化され、エンジニアがより高付加価値の判断に集中できる環境が整えられています。

シフトレフトとシミュレーションデータの増加

シフトレフト戦略は、設計サイクルの早期段階でテストと検証を行う考え方として重要です。これにより、物理的プロトタイプ作成前に潜在問題が検出され、後工程での修正コストや再設計リスクが最小限に抑えられます。タイミング解析、電力解析、熱解析、EMI/EMC解析など、各種シミュレーションデータの量は大幅に増加しており、最新のスケーラブルなDDMソリューションが求められています。各設計チームは必要なデータに迅速にアクセスでき、ネットワークストレージの負荷も軽減される仕組みが導入されています。

AIを活用した設計の革新

近年、AI技術が急速に発展し、AIベースのEDAツールが設計プロセスに革新をもたらしています。これらのツールは従来の手作業に依存したタスクを自動化し、設計空間の広範な探索や最適化を実現、エンジニアは高度な判断に専念できる環境となっています。機械学習アルゴリズムを用いたシミュレーションツールは、過去の設計データおよび実測データから学習し、最適な設計パラメータを自動提案することで、試行錯誤の回数を大幅に削減しています。また、AIによる異常検知やエッジケースの自動認識機能が、設計初期段階のリスク低減に寄与しており、全体の設計サイクル短縮と品質向上につながっています。

チップレットとヘテロジニアス統合の進展

チップレット技術およびヘテロジニアス統合は、従来の単一大規模チップ設計から、最適化された複数の設計ブロックを組み合わせる新たなパラダイムへとシフトしています。これにより、各機能ブロックが独立して最適化され、特定用途向けに柔軟に組み合わせることで、製品全体のパフォーマンスと効率が向上します。各ブロック間のデータ連携と設計検証はシームレスに行われ、統一されたDDMシステムの導入が必須となります。設計変更時の影響範囲が正確に把握され、全体の統合設計品質が保証される仕組みは、今後も技術進展と共に重要性が増すでしょう。

安全な設計データの確保

半導体設計において、設計データと知的財産の保護は極めて重要です。最新のDDMシステムは、アクセス制御、データ暗号化、ジオフェンシング、および多要素認証をはじめとする多層的セキュリティ対策を導入し、承認された担当者のみがアクセスできる環境を実現しています。これにより、情報漏洩リスクが大幅に低減され、国際的な輸出管理基準や各国のセキュリティ規制にも厳格に対応できる体制が構築されています。

設計データ管理ソフトウェアの重要性

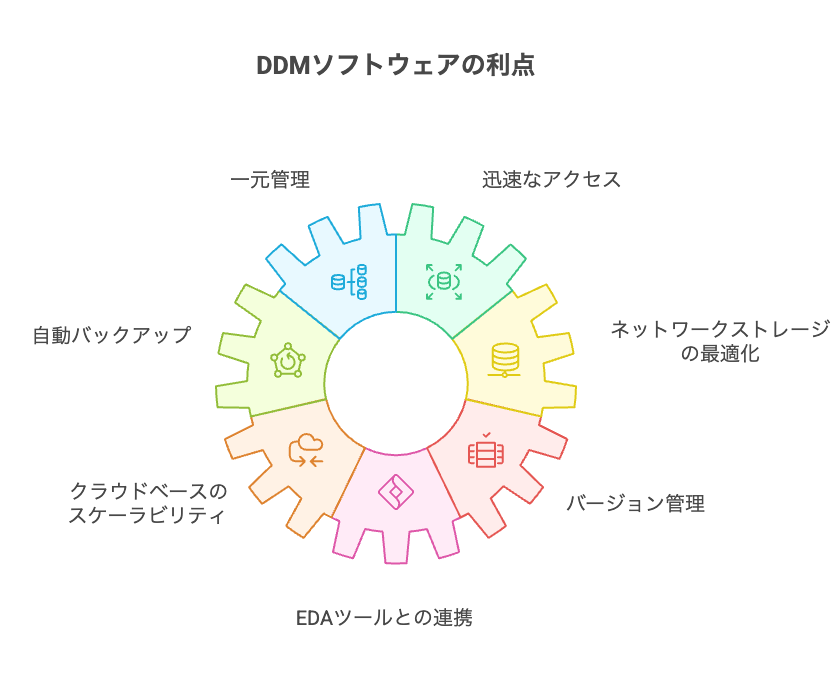

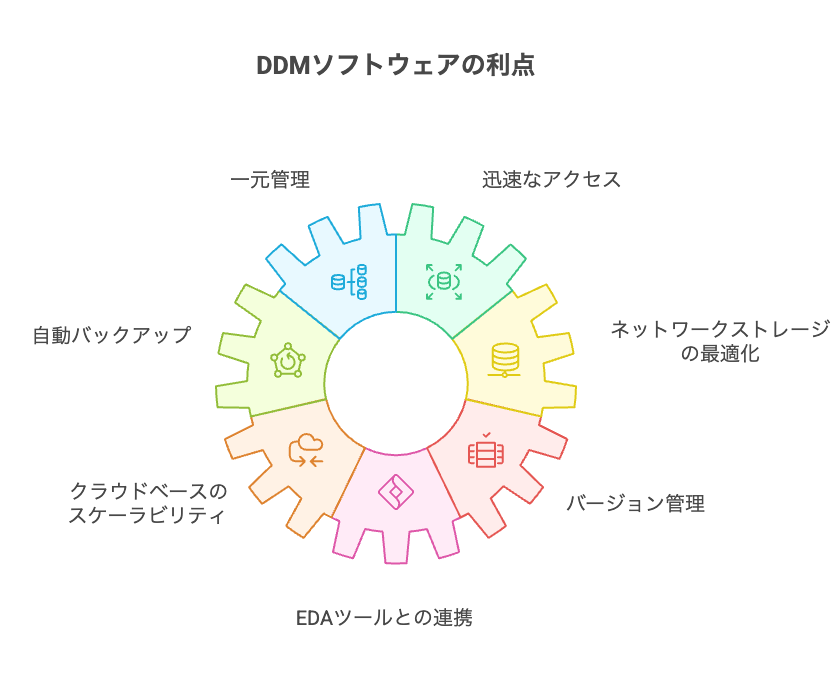

DDMソフトウェアの利点

効果的な半導体設計データ管理ソフトウェア(DDM)は、設計データの一元管理、迅速なアクセス、自動バックアップ、ネットワークストレージの最適化、クラウドベースのスケーラビリティなど数多くの利点を提供します。これにより、設計チームは常に最新のファイルにアクセスでき、正確なバージョン管理や変更履歴の追跡が可能となり、全体の信頼性と効率性が大幅に向上します。主要なEDAツールとの密接な連携により、設計から製造、品質管理に至る全プロセスで一元的なデータ連携が実現され、エラーの早期検出や迅速な問題解決に直結します。

マルチチームコラボレーションの促進

設計データ管理システムは、地理的に分散した拠点間や複数チーム間での情報共有を円滑にする基盤です。統一されたリポジトリとリアルタイムデータ同期により、各チームは常に最新・正確な情報に基づいて作業が進められ、設計変更や更新時の混乱が大幅に軽減されます。さらに、自動バックアップやキャッシュサーバーの導入により、どの拠点でも迅速なデータアクセスが保証され、これにより製品市場投入のスピードと企業全体の競争力が向上します。

ワークフローの統合

設計データ管理は、EDAツールのみならず、ERP、PLM、PDMなど他の業務システムと連携し、設計から製造、出荷、アフターサービスに至るまで統一されたデータフローを実現します。各システム間でのデータ一貫性が確保されることで、部門横断的なコミュニケーションが円滑になり、情報重複や不一致が大幅に削減されます。統合されたワークフローはまた、各プロセス進捗のリアルタイム分析を可能にし、迅速な意思決定をサポートする強力なツールとなっています。

設計トレーサビリティの強化

半導体設計は、多数のバージョン改訂や反復作業を伴います。最新DDMシステムは、概念設計からテープアウトまでの全工程における変更や承認プロセスを自動記録し、トレーサビリティを強化します。視覚的な差分ツールの統合により、設計段階ごとの変更点が直感的に把握でき、設計ミスの再発防止や迅速な原因究明が可能となります。これにより、国際安全基準への準拠も容易になり、全体の品質と信頼性が飛躍的に向上します。

IP再利用効率の向上

DDMシステムを活用することで、過去に検証されたIPブロックが効率的に管理・再利用できます。IPブロックへの参照リンク、更新履歴の自動管理、ライセンス情報の追跡により、既存設計要素の再利用が容易になり、新規設計の迅速化と設計ミス低減に貢献します。また、強固なセキュリティ対策により、知的財産が安全に管理され、企業の技術優位性を維持するための重要な資産となります。

データセキュリティとアクセス制御

設計データおよび知的財産は極めて機密性の高い情報です。最新DDMシステムは、アクセス制御、暗号化、ジオフェンシング、多要素認証など多層的なセキュリティ対策を実装し、承認された担当者のみがアクセスできる体制を整えています。これにより、情報漏洩のリスクが大幅に低減され、国際セキュリティ規制や輸出管理基準に準拠した堅牢な環境が実現されています。

半導体設計データ管理における新たな課題

業界が直面する6つの課題

高度な半導体設計データ管理の統合は、以下の6つの主要課題に直面しています。

- サイロ化された設計データシステム:各部署が独自システムを使用することで情報が孤立し、整合性が失われるリスク。

- バージョン管理の難しさ:頻繁な設計変更による複雑な改訂管理が困難となり、誤ったバージョン選択のリスク。

- ネットワークストレージの課題:大量データによるストレージ負荷増大とアクセス速度低下。

- コミュニケーションの障壁:地理的分散・タイムゾーン、言語・文化の違いによる情報共有の遅延。

- IPとデータセキュリティの確保:機密性の高い情報の保護対策の強化が必要。

- コンプライアンス要件の遵守:国際規格や業界標準に対応するための複雑な管理。

サイロ化された設計データシステム

設計チームが部門ごとに個別システムを使用すると、情報が各部署間で孤立し、データの整合性が損なわれるリスクが高まります。各種EDAツール、シミュレーションソフト、テスト機器によって生成される大容量バイナリデータは、従来のバージョン管理システムでは効率的な管理が難しく、設計変更時に統合が円滑に行われず、ミスや不整合が発生しやすくなります。最新DDMシステムは、異なるシステム間のシームレスなデータ連携とリアルタイム更新を実現し、情報の一元管理を可能にしています。

バージョン管理の難しさ

IC設計では、頻繁な変更によって各コンポーネントのバージョンが更新され、その管理が非常に複雑になります。従来のシステムでは大容量データの差分管理や変更履歴の追跡が不十分であり、誤ったバージョン選択のリスクが高まります。最新DDMシステムは、各設計変更を自動記録し、視覚的に分かりやすい差分ツールを統合することで、エラー再発防止と効率的な改訂管理を実現しています。

ネットワークストレージの課題

設計ライフサイクル全体で生成される膨大なデザインデータは、企業のネットワークストレージに大きな負荷をかけ、容量不足や管理コストの増大、さらにはアクセス速度の低下を引き起こす可能性があります。従来は各ユーザーがリポジトリ全体を複製する方式でしたが、最新DDMシステムはキャッシュサーバーやクラウドベースのソリューションを利用し、必要なデータのみをリアルタイムで同期する方式を採用しています。

コミュニケーションの障壁

設計現場では、世界中に散らばるエンジニアや異なる拠点での作業が増加しており、これにより、地理的距離、タイムゾーン、言語、文化といった要因が情報共有の障壁となっています。最新DDMシステムは、リアルタイム情報共有や自動化されたワークフロー、カスタムレビュー機能を通じて、効率的なコミュニケーションを促進し、各拠点の設計者が常に最新の情報にアクセスできる環境を実現しています。

IPとデータセキュリティの確保

知的財産や機密性の高い設計データは国家レベル・企業レベルで極めて高い価値を持つため、これらを守るためのセキュリティ対策は必須です。最新DDMシステムは、厳格なアクセス制御、暗号化、ジオフェンシング、多要素認証などの多層的セキュリティ機能を実装し、不正利用や情報漏洩のリスクを大幅に低減しています。

コンプライアンス要件の遵守

国際安全基準、業界標準、地域ごとの法規制に対応するため、各設計コンポーネントのライセンス状況、使用条件、規格の管理が必要です。統一管理体制により、各国の規制や業界標準に迅速かつ柔軟に対応でき、全体としてのデータ正確性と一貫性が保証されます。

設計データのアクセシビリティを向上させるための5つのベストプラクティス

データアクセシビリティと複雑性の管理

半導体設計データのアクセシビリティを向上させるため、以下のベストプラクティスが推奨されます:

- リポジトリの一元化:全設計データを一元管理されたシステムに保存し、唯一の真実のソースとする。

- キャッシュサーバーの導入と自動同期:各拠点でのデータアクセス速度を向上させ、低レイテンシビューの維持。

- 自動バックアップシステム:データ損失や破損のリスクを防ぐ。

- ネットワークストレージの継続的監視:リソース調整によりシステムパフォーマンスを最適化。

- クラウドソリューションの活用:オンプレミスを補完し、柔軟なスケーラビリティを実現。

設計データ管理の効率化は進めたいけれど、資料整理の第一歩が面倒…そんな悩みはありませんか?生成AI-OCRサービスなら、既存PDFカタログや技術資料から必要情報だけを抽出し、リポジトリ登録をスピードアップ。煩雑な資料整理からスタートするのは、もうやめにしませんか?一度試せば「もう戻れない!」という声多数です。

バージョン管理を簡素化するための7つのベストプラクティス

複雑な設計の効率的な管理

IC設計プロセスでは頻繁な変更や改訂が発生するため、以下の対策が有効です:

- 設計データの一元化:全エンジニアが最新ファイルにアクセス可能な単一プラットフォームを構築。

- 構造化されたバージョン管理ポリシー:セマンティックバージョン管理などを採用し、変更履歴を自動記録。

- チェックイン/チェックアウトの自動化:競合やデータ損失を防ぐ。

- 視覚的差分ツールの統合:変更箇所を直感的に把握。

- 承認ワークフローの合理化:変更前のレビューと承認プロセスを自動化。

- セキュリティ制御の実装:各ユーザーに適切な権限を付与。

- 設計および開発ツールとの統合:ツール間のシームレス連携を実現。

設計トレーサビリティを強化するための4つのベストプラクティス

IC設計プロセスの整合性と説明責任の維持

複雑なIC設計で変更履歴や承認プロセスの記録、ファイル変更の追跡を確実に行うため、以下の対策が推奨されます:

- 階層的なファイル整理:プロジェクトのワークフローに合わせたフォルダ構造を整備。

- 有益なメタデータの利用:プロジェクト名、変更日、設計パラメータ等を記録。

- ラベル付けの実装:変更内容、理由、承認状況を明確にする。

- 一貫したファイル命名規則:識別しやすい標準化された命名規則を採用。

Keysightで半導体設計データ管理を最適化する

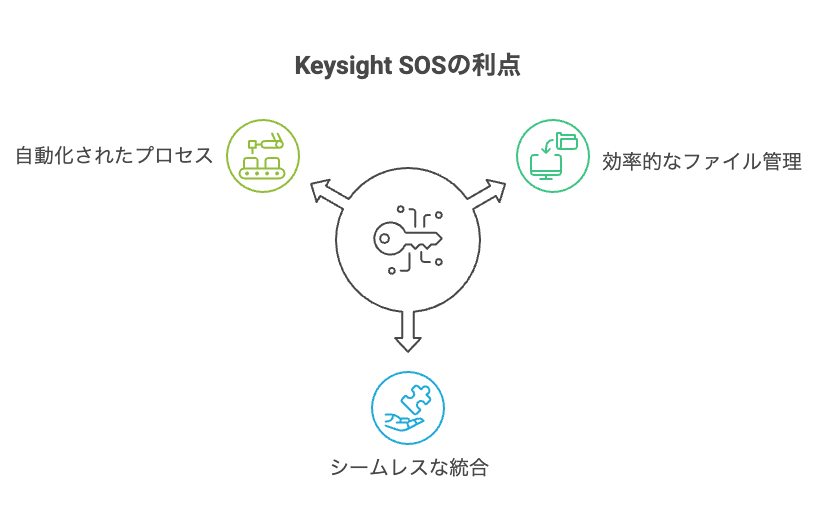

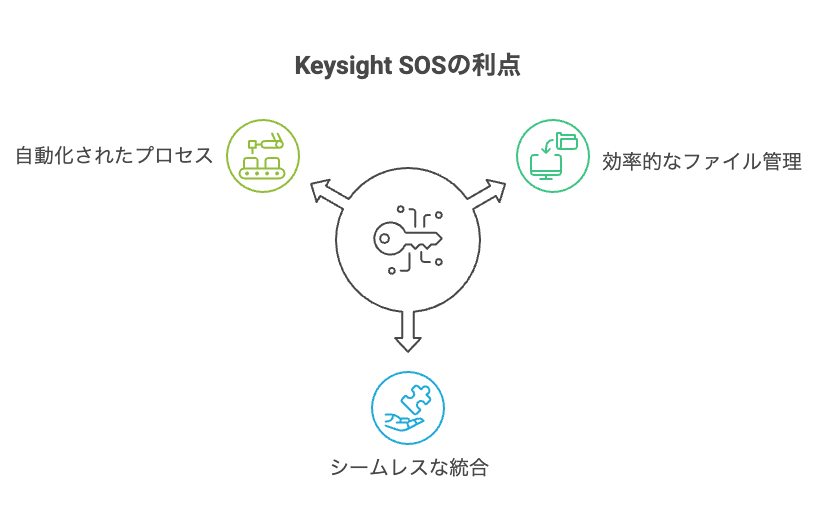

Keysight Design Data Management (SOS) の利点

Keysight Design Data Management (SOS) は、リライト元記事のベストプラクティスを包括的に実装し、20年以上の実績に基づいた信頼性あるツールです。SOSは、GDSファイルやシミュレーション波形などの大容量ファイルを効率的に管理し、キャッシュへのシンボリックリンク活用やスパースポピュレート機能によりユーザーのローカルおよびネットワークストレージ負担を大幅に低減します。主要なEDAツールとのシームレスな統合により、設計データの一元管理、改訂履歴の自動記録、承認プロセスの自動化が実現され、設計の品質と生産性向上に直結します。

大きな設計ファイルに最適なデータ管理

Keysight SOSは、従来のバージョン管理ツールが苦手とする大容量の設計ファイル、例えばGDS形式の物理設計データやシミュレーション波形などを効率的に管理するよう最適化されています。システムは、実ファイル自体を重複させず、シンボリックリンクで各ユーザーのワークスペースに参照させる仕組みを採用し、これによりストレージコストを大幅に削減しながら高速なアクセスを実現しています。また、各設計ファイルの変更履歴や改訂情報が自動記録され、リアルタイム更新されるため、設計のトレーサビリティが向上し、迅速な作業が可能です。

EDAツールとの統合とキャッシュへのシンボリックリンク

Keysight SOSは、Keysight Advanced Design System (ADS)、Cadence Virtuoso Studioなど主要EDAツールとシームレスに統合され、各ツールからの設計データを中央リポジトリで統一的に管理・共有します。さらに、ユーザーのワークスペースでは、メインリポジトリ上の実ファイルを指すシンボリックリンクが自動生成され、ファイルの重複なしにネットワークストレージの効率化と高速アクセスが実現されます。スパースポピュレート機能により、読み取り専用のデータブロックや大規模なIPライブラリも効率的に管理され、全体のシステムパフォーマンスが向上します。

効率的なIP再利用

Keysight SOSは、企業が蓄積した知的財産(IP)ブロックを効率的に管理し再利用するための機能を提供します。IPブロックの参照リンク作成、更新履歴やライセンス情報の自動管理により、既存の検証済みIPブロックの再利用が容易となり、新規設計にかかる時間とコストの大幅な削減につながります。再利用性の高い設計資産を有効活用することで、設計ミスの発生リスクも低減されます。

EDAデータのセキュリティ対策の強化

Keysight SOSは、最先端のセキュリティ対策を統合し、設計データおよび知的財産を保護します。アクセス制御、暗号化、ジオフェンシング、多要素認証など多層的なセキュリティ機能により、承認されたユーザーのみのアクセスを厳格に許可し、不正なデータ流出を防止します。これにより、企業は国際セキュリティ規制や輸出管理基準にも確実に準拠可能です。

高度な改訂管理

Keysight SOSは、設計データの改訂管理において高度な自動記録システムを導入しています。各設計変更がリアルタイムでログとして記録され、リリースおよび派生設計が厳格に管理されるため、変更点の追跡が容易になり、設計ミスの再発防止と効率的な問題解決が実現されます。さらに、問題追跡ソフトウェアとの連携により、設計変更の影響範囲評価が迅速に行われ、全体の品質向上に寄与しています。

半導体設計データ管理の最新動向

最新の設計データ管理ソリューション

半導体設計データ管理分野は急速な技術革新に伴い、最新ソリューションが続々と登場しています。これらのシステムは、設計プロセス全体の効率化と一元管理を実現するため、柔軟性とスケーラビリティを兼ね備えており、従来のオンプレミス型からクラウドベースの管理システムへとシフトしています。これにより、リアルタイムでのデータ解析、統合管理、災害復旧計画の強化が実現され、設計コストの削減と市場投入までの期間短縮が可能となっています。

クラウドベースのデータ管理

最新の半導体設計データ管理では、クラウドベースのシステムが主流となり、オンプレミス型の制約を大幅に解消しています。クラウド環境では、需要に応じたスケーラブルなリソース提供、災害復旧能力向上、グローバルなアクセス性が確保され、地理的に分散した設計チーム間でも常に最新データにアクセス可能です。これにより、設計データの一元管理、リアルタイム更新、解析が可能となり、全体の効率性と生産性が向上しています。

リアルタイムデータ分析の導入

最新の設計データ管理ソリューションでは、リアルタイムデータ分析技術が積極的に導入されています。シミュレーションデータ、動作状況、製造プロセス中の各種パラメータが即時に解析され、設計過程での微細な変動やエラーが早期に検出される仕組みが整えられています。これにより、設計者は迅速に改善策を講じることができ、製品の品質と信頼性が大幅に向上します。

セキュリティ強化のための新機能

半導体設計データ管理におけるセキュリティは、ますます重要視されています。最新ソリューションは、従来のセキュリティ対策に加え、データ暗号化、リアルタイムアクセス制御、ジオフェンシング、多要素認証、そして高度なログ解析などの新機能を統合し、設計データと知的財産を不正アクセスやサイバー攻撃から守るための堅牢な防御体制を構築しています。

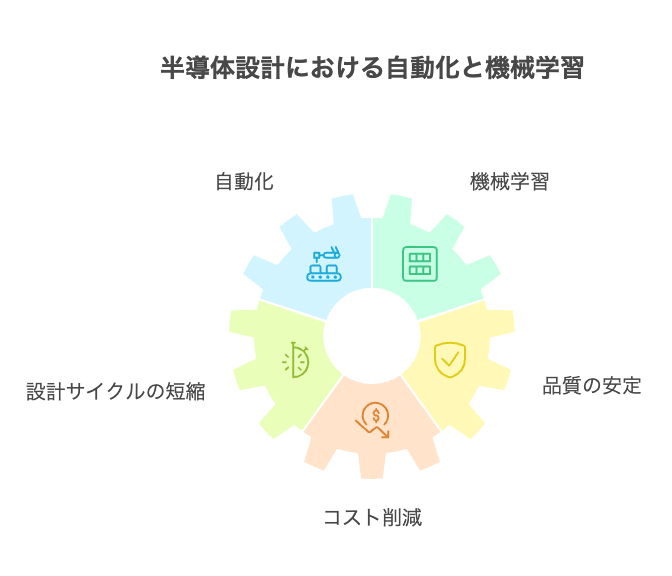

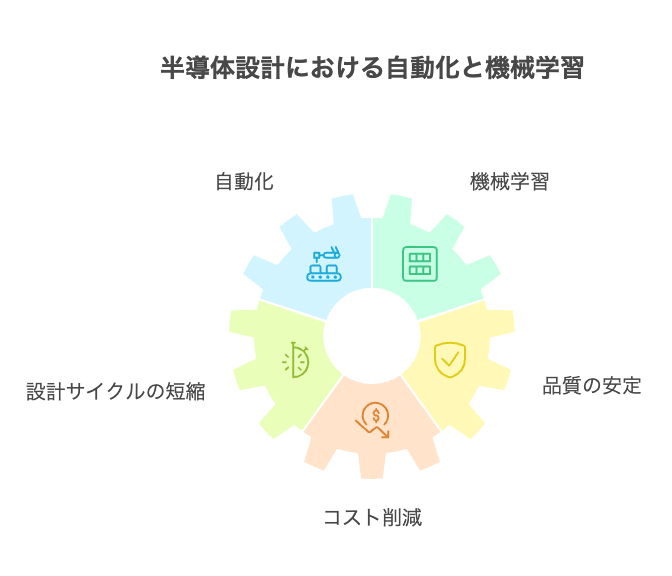

自動化と機械学習の活用

近年、半導体設計プロセスにおいて、自動化と機械学習の導入が革命的な変化をもたらしています。多数の反復作業やパターン認識、設計上の異常検知が自動化され、エンジニアはより創造的な問題解決に集中できる環境が整えられています。機械学習は、大量の設計・解析データから傾向やエラーを予測し、将来的な設計改善の指針を提示するなど、設計サイクルの短縮や品質の安定、コスト削減に大いに寄与しています。

まとめ

本記事では、リライト元記事に基づいて、半導体設計データ管理の基礎から最新動向、各種ベストプラクティス、主要な課題、そしてKeysight SOSの具体的な優位性について解説しました。以下のポイントが特に重要です:

- 一元管理とリアルタイム更新による効率向上

- セキュリティ強化と適切なバージョン管理の必要性

- 複雑な設計プロセスにおけるチーム間の連携強化

- クラウド環境やAI、機械学習の活用による最新ソリューションの導入

- 各企業(ファブレス、IDM、OEM、EDA/IPベンダー)の役割と連携の重要性

これらの対策、具体例、最新技術を通じて、半導体設計の効率性、品質、そして市場競争力の向上が実現されることが期待されます。